ISSN: 2349-7947 28 - 31

# Logical Control of Permanent Magnet Brushless DC Motor

Mukesh Kumar Kumawat PhD Scholar JJT University, Jhujhununu, Rajasthan , India Email - mbkumawat12@gmail.com Dr. Rajesh kumar Rai Professor (Dean ) NIRT Bhopal MP Bhopal , MP India Email- raj.rai1008@gmail.com

Abstract- The paper presents the simplest method for dominant the speed of PMDBLDC motor in which the switch of 3-Φ Bridge is completed by the output of hall sensors themselves. This is achieved by giving the output of hall sensors to the combinational logic circuit that decides the switch combos for electronic commutation of PMBLDC motor. For controlling the speed of motor the gate pulses of higher 3 switches area unit modulated exploitation PWM technique and then fed to the motive force. The PWM technique gives the swish variation of input voltage to the motor for dominant the speed.

Keywords -PMBLDC, MD, PWM, CL, OL etc.

### 1. INTRODUCTION

Today most of the techniques applied for dominant the speed of PMBLDC motor use high speed computers, fast processors, dedicated controllers and digital signal processors which area unit very pricey so thus several time the price of controller card has been found rather more higher than that of the motor to which the speed management is applied, at the same time this techniques use complicated programming and need masterful operator. When the shut loop operation is needed these techniques area unit required, but in some applications the open loop management of motor is enough, (i. e. battery operated two wheelers, cars, and in home appliances) at that time some simple and user friendly technique should be developed. In this paper we've got tried to develop a really simple technique to cut back the price of controller card employing a combinatory logic circuit. This is open loop control and extremely user friendly

## 2. CONSTRUCTION OF PMBLDC MOTOR-

The basic parts of PMBLDC motor area unit 1. Stator 2. Rotor 3. Hall sensor

Figure 1. PMBLDC Motor.

A brushless dc motor is a dc motor turned inside out, so that the sphere is on the rotor and also the armature is on the mechanical device. The brushless dc motor is actually a magnet ac motor. Instead of commutating the armature current exploitation brushes, electronic commutation is used. Some BLDC motors have armature windings on the interior shaft

and also the magnet on the outside enclosure that rotates, thus it is AN inverted BLDC. These types of motors area unit used for battery operated 2 wheelers. In our project we area unit exploitation the same sort of motor. Three Hall position sensors area unit used to verify the position of the rotor field. These particular Hall position sensors, based on Hall impact principle, generate a TTL compatible output. Hall sensors area unit mounted in mechanical device in such a manner that once they are coated by magnetic "N" pole they conduct.

### 3. HALL ANALYZERS-

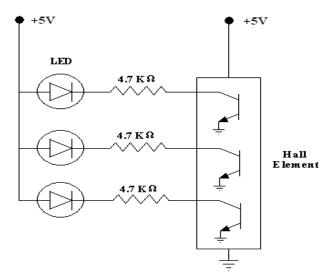

Very initial step for planning the feedback circuit for BLDC motor is to investigate the sequences of hall sensors. The hall sensors are open collector icon transistors. The hall sensor can conduct when it is coated by magnetic "N" pole and remains off in alternative cases. In our project for analyzing hall sequence we have used this circuit.

Figure 2. Hall sequence analyzer

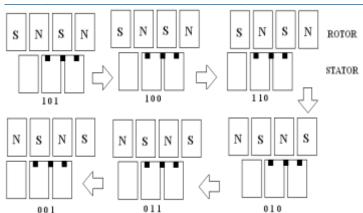

The hall sensors area unit mounted on mechanical device such that most 2 hall sensors are coated by "N" Pole and at least one hall sensor remains beneath the influence of "N" pole at any time. So with the given circuit and theory the hall sequence for the motor that we area unit having is as beneath.

Figure 3.Rotor positions for six different hall sequences.

As 48 poles area unit there in our motor these sequence can repeat once every 15° (mechanical)rotation. So the distinction in degree between 2 consecutive sequences is two.5° (mechanical) Therefore you extremely have to be compelled to watch out whereas analyzing hall sequence manually by rotating motor shaft.

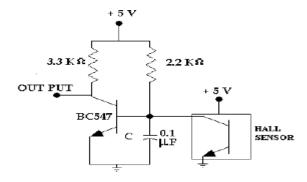

### 4. HALL DECODER

With the above circuit we have a tendency to can simply get the concept concerning hall sequences however we will not use this sequence for logical operation. For using these hall sensors output with logic gates we have a tendency to would like to provide a pull-up circuit to every hall part. This pull-up circuit is known as hall decoder. The circuit that we area unit exploitation is given below.

Figure 4. Hall decoder

The operation is very easy. When the hall device is not active, base of semiconductor unit Q1 is "HIGH" and Q1 is "ON" and the output of Q1 that is taken from the collector of the transistor is "LOW". Similarly once the hall part is active, the base of Q1 is "LOW" and also the Q1 is "OFF" and the output of Q1 is "HIGH".

# 5. IDENTIFICATION OF SWITCH COMBINATIONS

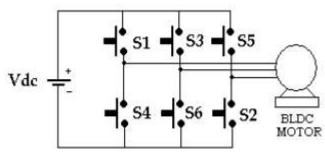

After secret writing the hall sequences the vital factor is to decide good switch pattern per hall sequence for proper electronic commutation. In our project we have used  $3-\Phi$  Bridge using six push-button switches (2 A type) to perform this operation.

Figure 5.Switch matrix.

At each and each hall sequence there area unit six potential switch combos. For example Present hall sequence is one zero one and the potential switch combos area unit 1&2, 2&3, 3&4, 4&5,5&6, 6&1. Out of these six combos solely 2 combos area unit correct for that 2 combinations the motor can rotate once in one direction then in reverse direction. The simple technique is to start out with anybody hall sequence and check out completely different switch combos and there'll be one combination for that the motor rotates in one direction and brakes at the purpose wherever successive hall sequence comes. In the same way for one switch combination the motor rotates in reverse direction and brakes at the purpose wherever the previous hall sequence can return. For the other switch combos motor rotates however brakes at bound purpose at that time the hall sequence won't be successive or previous to this hall sequence. After characteristic one correct switch combination at one hall sequences alternative 5 combos area unit terribly state forward.

The switching pattern matches with that of  $3-\Phi$ ,  $120^\circ$  conduction mode electrical converter. According to this theory the reality table for proper switch combinations at completely different hall sequences area unit as below. Table.1 Switch combination for six hall sequences Hall sequence Switch combos A B C Forward direction Reverse direction

| Hall sequence |   |   | Switch combinations |           |  |  |

|---------------|---|---|---------------------|-----------|--|--|

| A             | В | С | Forward             | Reverse   |  |  |

|               |   |   | direction           | direction |  |  |

| 1             | 0 | 1 | S2, S3              | S1, S6    |  |  |

| 1             | 0 | 0 | S3, S4              | S1, S2    |  |  |

| 1             | 1 | 0 | S4, S5              | S2, S3    |  |  |

| 0             | 1 | 0 | S5, S6              | S3, S4    |  |  |

| 0             | 1 | 1 | S6, S1              | S4, S5    |  |  |

| 0             | 0 | 1 | S1, S2              | S5, S6    |  |  |

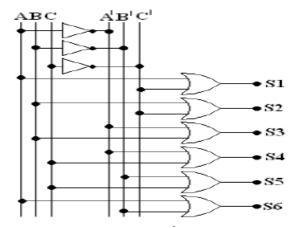

### 6. DESIGN OF COMBINATORY LOGIC

According to the above switch combos the reality table for 6 gate pulses area unit as below. As we have used the well-known "International Rectifier" created three-phase electrical converter bridge driver IC "IR2130" that has all the six inputs (HIN1, 2, 3 and LIN1, 2, 3) which area unit active low kind and the output is out of section with input so for creating any switch "ON" the in place pulse for that switch should unbroken "LOW" and once the in place pulse at any input of driver is "HIGH" the various switch remains "OFF". According to the necessities the reality table for forward

operation of motor is given below. According to the above truth table the logical expressions for all six gate pulses area unit as shown below. The combinational logic diagram per this logical expression are often enforced with the assistance of NOT and OR gates. The complete logic diagram is shown below. Table.2 Truth table for switch 3- $\Phi$  Bridge. Hall sequences Switches of 3- $\Phi$  bridge

| Hall sequences |   |   | Switches of 3-Φ bridge |    |    |    |            |    |  |

|----------------|---|---|------------------------|----|----|----|------------|----|--|

| A              | В | С | S1                     | S2 | S3 | S4 | <b>S</b> 5 | S6 |  |

| 1              | 0 | 1 | 1                      | 0  | 0  | 1  | 1          | 1  |  |

| 1              | 0 | 0 | 1                      | 1  | 0  | 0  | 1          | 1  |  |

| 1              | 1 | 0 | 1                      | 1  | 1  | 0  | 0          | 1  |  |

| 0              | 1 | 0 | 1                      | 1  | 1  | 1  | 0          | 0  |  |

| 0              | 1 | 1 | 0                      | 1  | 1  | 1  | 1          | 0  |  |

| 0              | 0 | 1 | 0                      | 0  | 1  | 1  | 1          | 1  |  |

Figure 6.Combinational logic for six gate pulse

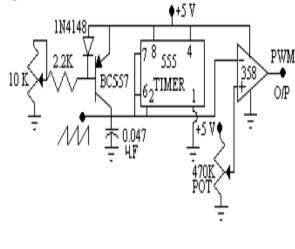

### 7. PWM TECHNIQUE-

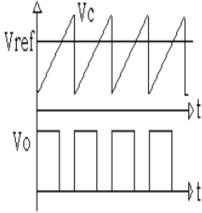

The speed of PMBLDC motor is controlled by controlling its input voltage that is potential by using a step down chopper before electrical converter, but AN introduction of AN further switch can build the planning difficult and at an equivalent time further feedback circuit is required for dominant that switch. To overcome these problems we are going to apply PWM technique directly in electrical converter circuit and for achieving that we are going to apply PWM technique to the gate pulses of higher 3 switches (S1, S3 and S5) of 3-Φ Bridge. For generating PWM signal we have used 2 circuits one as a high frequency saw-tooth wave generator and second as a magnitude comparator .A 555 timer and a perfect combination of RC circuit area unit accustomed generate saw tooth wave. The charging circuitry consists of one PNP semiconductor unit BC557 and a quick switch diode 1N4148. The charging time will be modified by dynamical the predetermined of 10K connected asynchronous with the bottom circuit of the semiconductor unit by that you just can amendment the frequency of the saw tooth wave. The duty ratio of the output signal are often controlled by dynamical the DC reference voltage at the non-inverting input of the comparator. For changing DC reference voltage we have a tendency to have used 470K pot. The circuit diagram and the relevant wave forms are shown in figure below.(a) (b)

Figure 7. (a) PWM circuit (b) PWM output

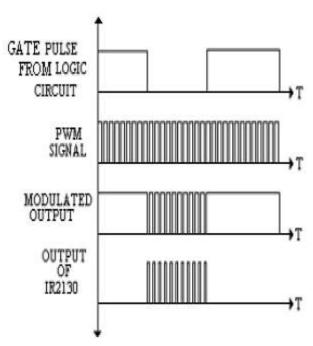

The PWM output of the comparator is given as an input to OR gates. The gate pulses of upper three switches area unit given as second input to the higher than OR gates and the output of the OR gates will represent the total of basic gate pulse and the PWM signal. The operational diagram and the relevant wave form area unit shown in figure below. (a) ,(b)

# G1 TO THE INPUT PINS (HIN1,HIN2,HIN3) OF IR2130

Figure 8. (a) Combination logic for PWM

Figure 8 (b) Modulated PWM output.

### 8. 3-Φ BRIDGEAND DRIVER CIRCUIT -

As explained earlier we have used IR2130 six steps, 3-Φ Bridge driver as a switch driver. The  $3-\Phi$  Bridge consist of six MOSFETs IRF540N 100V, 33A as electronic switches. The connection Diagram is shown in figure.

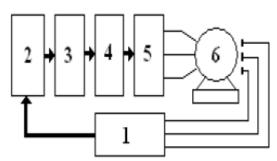

### 9. WORKING-

Figure 9. Block diagram for open loop logical control of PMBLDC motor. Phase-to-Phase Voltage starting with motor in standstill condition and the PWM pot is in such position that everyone the six pulses area unit high and every one the output gate signals of driver IC IR2130 area unit low. Now slowly flip the PWM pot and any 2 gate pulses according to the hall sequence can go LOW and that they remains LOW for a time throughout that the PWM signal is LOW which can build any 2 switches ON and motor can get some reduced dc voltage and at some instant the motor can turn out enough force and can begin rotating. Now adjusting the pot at completely different position you will see the amendment in speed of the motor. For turning off the motor set the pot to a minimum position (fully anticlockwise) and switch off the facility supply.

Figure 9.Block diagram of PMBLDC Motor

### 10.CONCLUSION

In this paper we've got tried to develop a really simple technique to cut back the price of controller card using a combinatory logic circuit. This is open loop control and extremely user friendly. This technique can be used wherever the open loop management is enough, like battery operated vehicle and home appliances

### REFERENCES

- [1] "Six-Output 600V MGDs Simplify 3-Phase Motor Drives", International Rectifier, Application Note AT-985

- "Implementation of a Sensor less Speed Controlled Brushless DC Drive Using TMS320F240", Houston, TX: Texas Instruments, Literature no. BPRA072, Nov. 1997.

- [3] "LM 358", www.national.com, Santa Clara, CA: National Semiconductor, accessed Oct. 2003.

- [4] N. Mohan, T.M. Undeland, and W.P. Robbins, Power Electronics Converters, Applications, and Design, New York: John Wiley & Sons, 1995.

- [5] S.P. Waikar, "A low-cost low-loss brushless permanent magnet motor drive", Ph.D. dissertation, Texas A&M University, College Station, TX, May 2001.

- [6] T. Kenjo and S. Nagamori, Permanent-Magnet and Brushless DC Motors, Oxford: Clarendon Press, 1985.

- [7] Adams, "Bootstrap Component Selection For Control IC's", International Rectifier, Design TipDT98-2

- [8] "Gate Drive Characteristics and Requirements for HEXFET®s", International Rectifier, Application Note

- [9] S. Clemente, et al., "Understanding HEXFET® Switching Performance", International Rectifier, Application Note

- [10] V. Barkhordarian, "Power MOSFET Basics", International Rectifier, Technical Paper

- [11] K. Dierberger, "Gate Drive Design for Large Die MOSFETs", PCIM '93, Reprinted as Advanced Power Technology, Application Note APT9302

- [12] "HV Floating MOS-Gate Driver ICs", International Rectifier, Application NoteINT-978

- [13] T. J. E. Miller, Brushless Permanent-magnet and Reluctance Motor Drives. CLARENDON PRESS. OXFORD. 1989.

- [14] SUNPLUS, 3-Phase BLDC Motor Control with Hall Sensor.

- [15] M H V Patel ,"Open loop logical control of PMBLC Motor" APE 09, National Institute of Technology, Rourkela – 769008, Orissa.